集成电路设计的开源EDA软件Yosys

2023-04-07 来源:文库网

集成电路设计的开源EDA软件Yosys

本文核心词:芯片,EDA,集成电路,集成电路设计,芯片设计,芯片设计开源软件EDA,集成电路设计软件EDA,开源EDA,集成电路开源设计软件,芯片设计软件EDAYosys是verilogrtl综合的一个框架。它目前拥有广泛的Verilog-2005支持,并为各种应用领域提供了一套基本的综合算法。选定功能和典型应用:

处理几乎所有可合成的Verilog-2005设计

正在将Verilog转换为BLIF/EDIF/BTOR/SMT-LIB/simple RTL Verilog/etc。

用于检查属性和等价性的内置形式化方法

映射到ASIC标准单元库(Liberty文件格式)

映射到Xilinx 7系列和Lattice iCE40 FPGA

自定义流的基础和/或前端

YOSYS可以通过使用合成脚本组合现有的通行(算法),并通过扩展YOSYS C 代码库来添加额外的通道来执行任何合成任务。

Yosys是一种基于ISC许可证(一种与GPL兼容的许可证,与MIT许可证或2条款BSD许可证类似)授权的自由软件。

Yosys 是2012年开始的项目,至今还在更新(cliffordwolf/yosys · GitHub)

自带一个cmos的标准库,类似于Synopsys GTECH

它的内部库映射算法使用的是 Berkeley ABC ABC: A Simple System for Sequential Synthesis and Verification

最新的(OSX 10.10 XCode 6.1)可以编译通过,只需打开Makefile中的clang选项即可

这个小玩意儿足以胜任集成电路综合的教学任务(EDA工具教学的部分除外)

示例用法

Yosys使用合成脚本进行控制。例如,下面的Yosys合成脚本从verilog文件mydesign.v读取一个设计(顶部模块为mytop),并使用Liberty文件中的单元库将其合成为门级网络列表迈锡尔.lib并将合成结果作为Verilog netlist写入synth.v:

# read design

read_verilog mydesign.v

# elaborate design hierarchy

hierarchy -check -top mytop

# the high-level stuff

proc; opt; fsm; opt; memory; opt

# mapping to internal cell library

techmap; opt

# mapping flip-flops to mycells.lib

dfflibmap -liberty mycells.lib

# mapping logic to mycells.lib

abc -liberty mycells.lib

# cleanup

clean

# write synthesized design

write_verilog synth.v

synth命令提供了一个良好的默认脚本,可作为简单合成脚本的基础:

# read design

read_verilog mydesign.v

# generic synthesis

synth -top mytop

# mapping to mycells.lib

dfflibmap -liberty mycells.lib

abc -liberty mycells.lib

clean

# write synthesized design

write_verilog synth.v

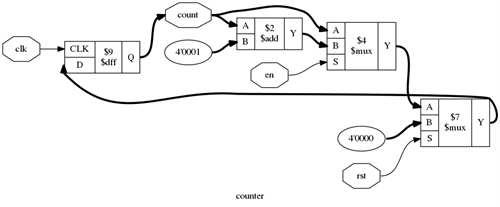

截图

这个页面包含简单的Yosys合成脚本的例子,以及合成设计的“show”命令输出的屏幕截图。(“show”命令使用GraphViz生成示意图。)

简单RTL网络列表

# read design

read_verilog counter.v

hierarchy -check

# high-level synthesis

proc; opt; fsm; opt; memory; opt